430mhz 1kw SSPA (3)

- 2017/10/26 15:03

- カテゴリー:SSPA, 432MHz 1KW SSPA for EME

さて今回からは少し実機の進捗具合を。。。

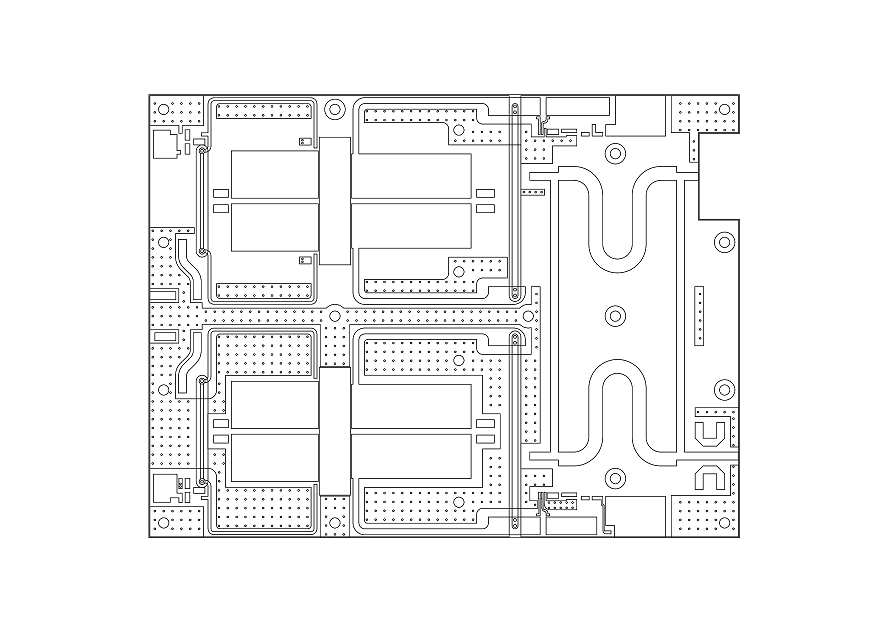

回路シュミレーション結果から起こしたPCBのパターン図です。面倒なので一気に入力側分配器と出力のブランチラインカプラ(90°合成器)用のパターンも1枚のPCB上に配置してしまっています。入力側分配器は90°のチップカプラを使う予定です。試作基板ですのでレジスト類は塗布していませんが、最終版ではレジスト、シルクは入れる予定です。

PA部分の整合回路のグランドパターンが上下のデバイスで違うのは、グランドパターンとマイクロストリップラインとの間隔がRF特性に与える影響を確認するためで、あえて2種類のパターンを作成して比較実験をする予定でいます。

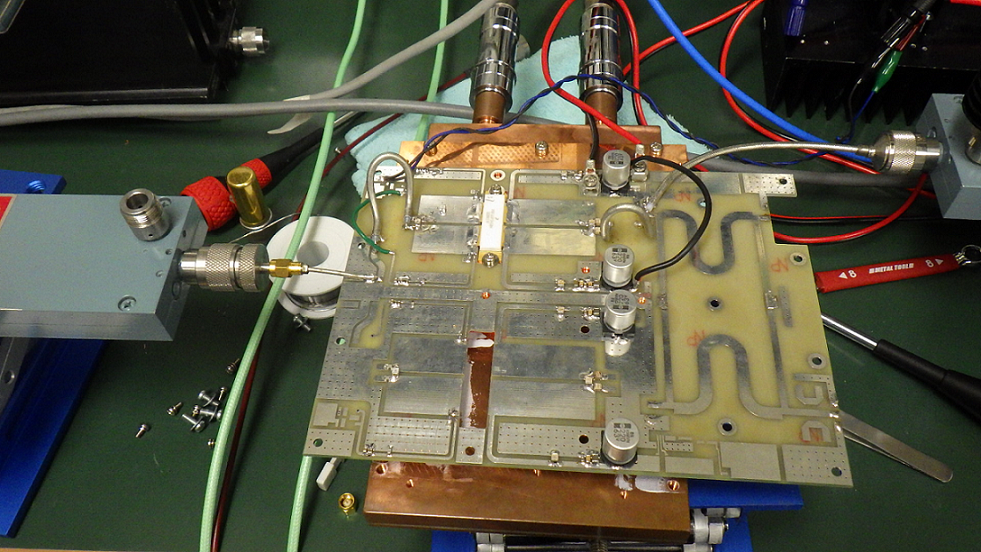

試作PCBの実験の模様です。入出力のRFラインと電源しか配線していませんが、PCB上にはドレイン電圧のオン/オフ用のFETスイッチや電流検出用抵抗のパターンなどもレイアウトはしています。ただ、ゲートバイアスの温度補償回路は乗せていませんので、今後追加する予定です。

試験自体は増幅部のみで分配/合成器は動作させていません。出力側のピックアップケーブルのロスは結構あるかもしれません。

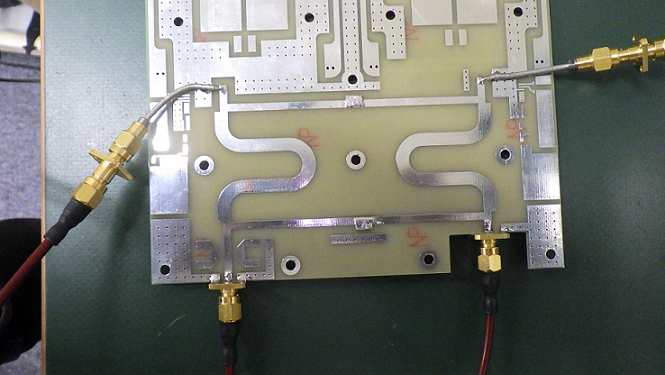

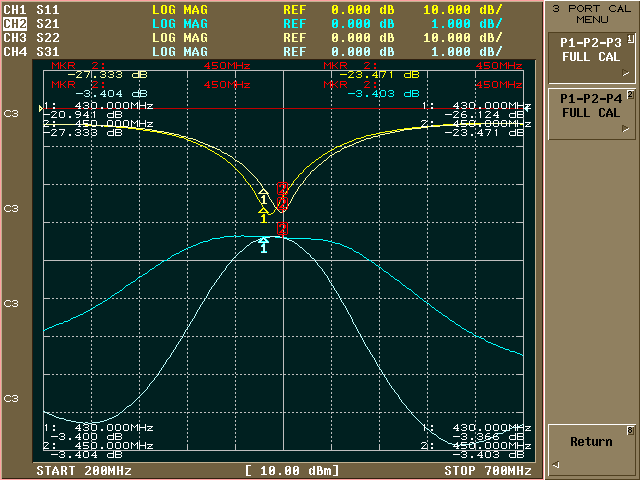

出力合成器部分のアップと実測データです。

入出力ポートの引き出しケーブルのロス込みで0.4dB程度の挿入損失ですので、カプラ自体での挿入損失は0.2dB程度ではないかと思われます。ただ、0.2dBでも約5%のロスになりますので、仮に片側のPAが500W出力とすると25Wがパターン上で消費されますので、この部分は放熱器に密着させる事が必要です。

各入力ポートのIRLは20dB以上は確保できていますので、PAの負荷としては上出来ではないでしょうか。

合成器の高インピーダンスラインでスタブで周波数特性、挿入損失の調整をしています。このスタブによってS21とS31を合わせこんでいますが挿入損失の低減よりも各入力ポートからのバランスを重視しています。パターン的にはチップコンデンサを乗せる事も可能にしてありますが、試作基板で再現性を確認して最終バージョンではパターン化したいと思います。