430mhz 1kw SSPA (5)

- 2017/10/31 16:43

- カテゴリー:SSPA, 432MHz 1KW SSPA for EME

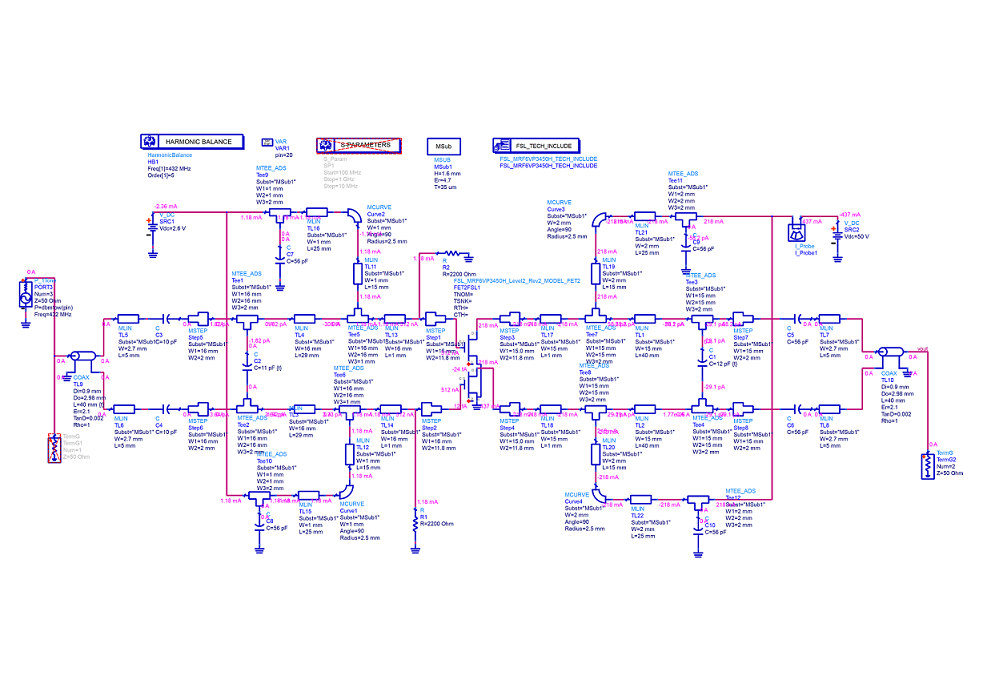

プッシュプル増幅器には必須のバラン(180°位相変換器)とPAのIRLがRF特性(主に飽和特性)に与える影響について少し実験してみました。

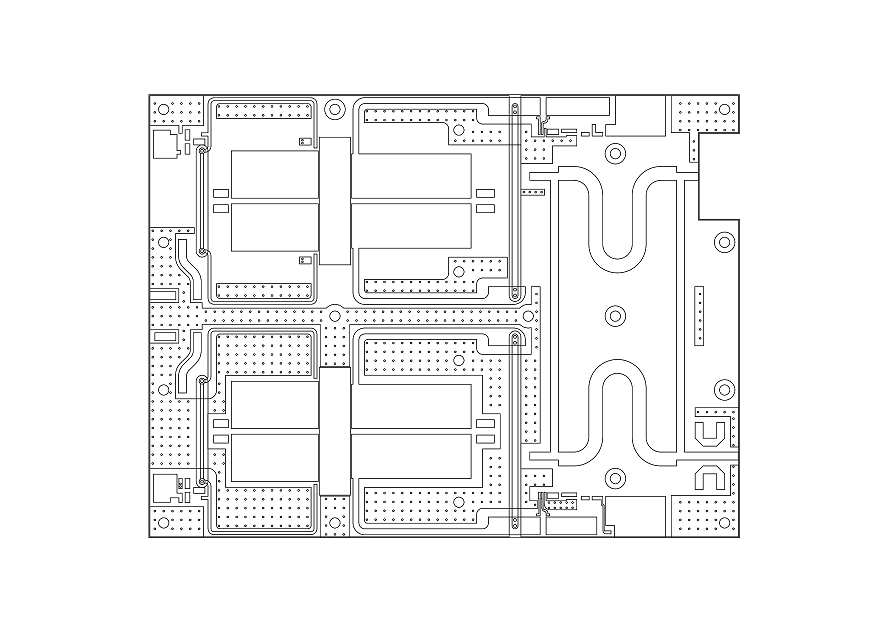

180°位相シフトさせるためには色々な手法があります。例えば、180°位相が遅れる位相ラインをプッシュプルペアの片側のラインに追加する等です。ただし、この方法は高周波数で使用しないとマイクロストリップラインの物理長(25Ω→50Ωへのインピーダンス変換のためのアディショナルな1/4λ線路が必要になるため)が長くなってしまうため実装面積が大きくなってしまいます。

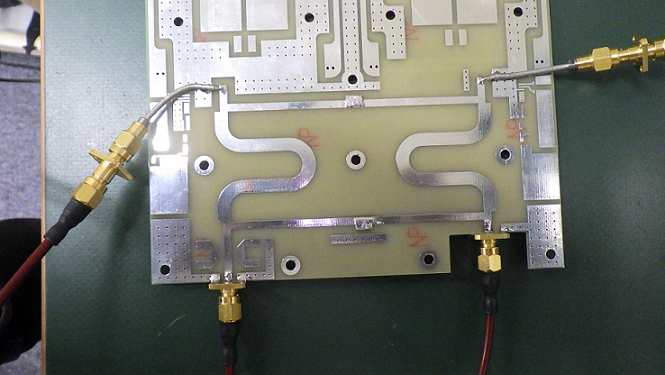

他には一般的に『バラン』と呼ばれるトランス方式の物です。本来はバランを作成するためには3本の線路が必要です。テキスト通りPAにも2本の同軸ケーブルを向かい合わせに接続して製作している物も多々あります。

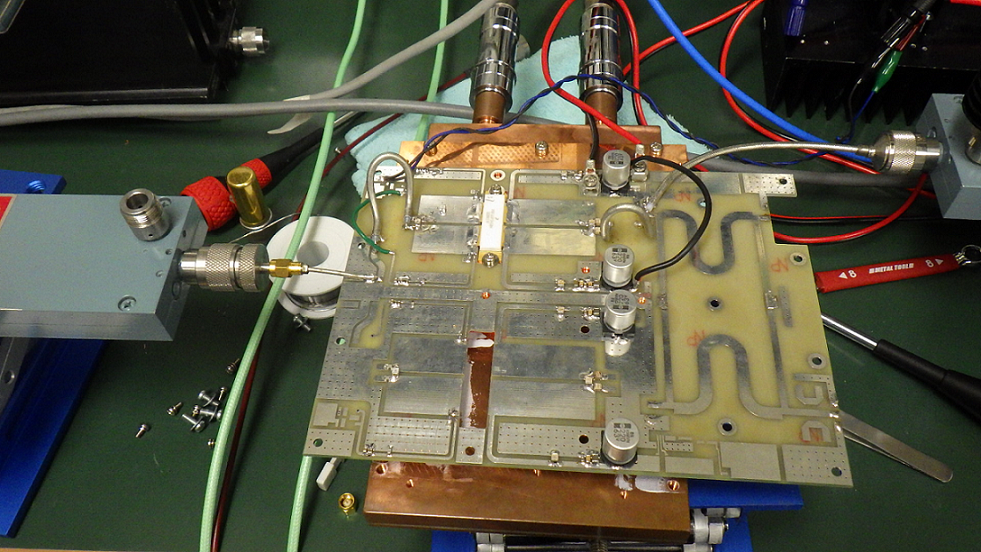

しかし、今回は簡易的に1本の同軸ケーブルで入出力バランを構成しています。

通常バランを作成する場合には線路長は1/4λとします。今回はセミフレキシブルケーブルを使用していますので、ケーブル内の絶縁体はPTFEで誘電率ε=2.1となり、波長短縮率は約69%となります。432MHzで計算すると約120mmの長さという事になります。実際にはバランの外側導体はPCBのグランドパターンの影響を受けると思いますし、バランをPCB上のパターンにハンダ付けする場合にハンダ付け部分の長さはどう考えるのか等、色々と悩む部分でもあります。このバランの長さがどの程度PAの特性に影響を与えるか検証した結果です。

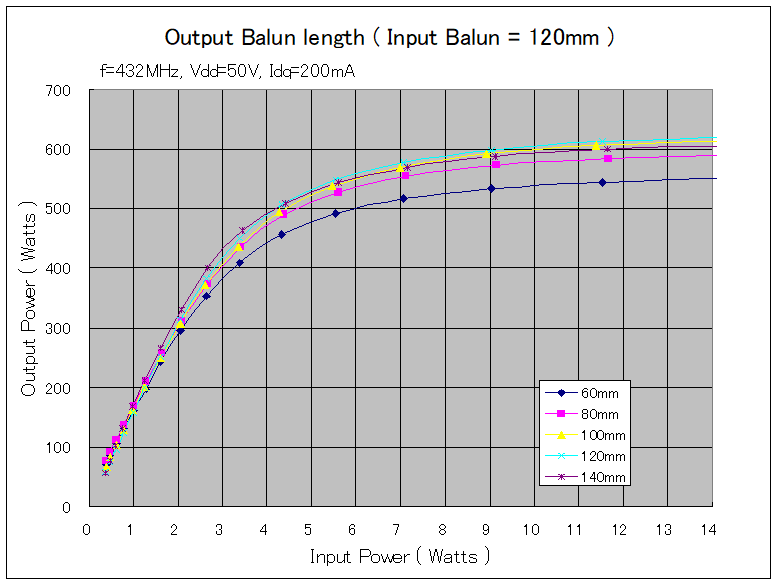

まず主に影響するであろう出力側バラン長を60mm(計算結果の半分の長さ=1/8λ)~ 140mmまで20mmステップで変えてみました。60mmとしたのは、以前実験した時に1/8λ程度でもアンプ自体は動作するのですが、理想値からどの程度特性劣化があるのかの確認です。今回のPAはUHF帯用でバラン長もさほど長くないので特に問題でありませんが、VHF帯用(50MHz/144MHz)などではバランの物理的な処理に困りますのでついでの確認です。ただし50MHz以下はフェライトコアを使った広帯域トランスですので、また違う世界ですね。

このデータではバラン長の最適値(計算値)=120mmで出力500W(大体P1dB+α近辺です)で比較した場合、バラン長=60mm(1/8λ)では約50W程度の出力低下が見られます。ゲインも全体的にそれなりに低いようです。

しかし、最適値の120mmに対して線路長はクリチカルか?と言われれは、そうでもないようで、±20mm程度の差であれば特性的には誤差範囲ではないかと思われます。バランの実装上40mmの長さはレイアウトを考えると結構効いてきますで、±20mm(40mm長)の長さの範囲で最適なレイアウトを選択しても良いと思われます。

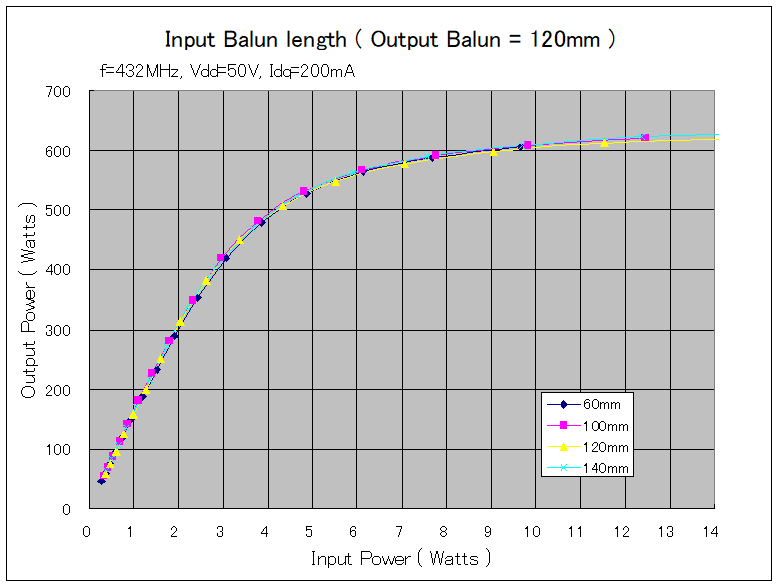

同様に出力側のバラン長を最適値(120mm)に固定して入力側バランの長さを変えてみました。

入力側に関しては出力側と違って長さの影響はほとんど確認できませんでした。ただし、今回使用したデバイスがデータシートスペックでもIRLが非常に悪いため、その影響かもしれません。実際、IRLの数値データも取得しているのですが、出力の増加(入力が増える)にしたがってIRLが悪くなっていく状態です。調整時にネットワークアナライザで小信号でのIRLを調整をしているための問題と思われます。最終的には小信号時ではなく大信号でIRLが最良となるようにしなければならないのですが、まだそこまで手が回っていません。IRLの目標は一般的には-10dB以下(できれば-17dB程度)が良いのですが。RF LDMOSの場合にはそこまでシビアに考える必要は無いと思っています。今回のPAの場合には実際には入力には2分配器は入りますので、ドライブ用の無線機の負荷には入力分配器のIRLが見えます。実際には入力リレーや必要に応じて追加する入力アッテネータを含んでのIRLがPA自体のIRLとなります。

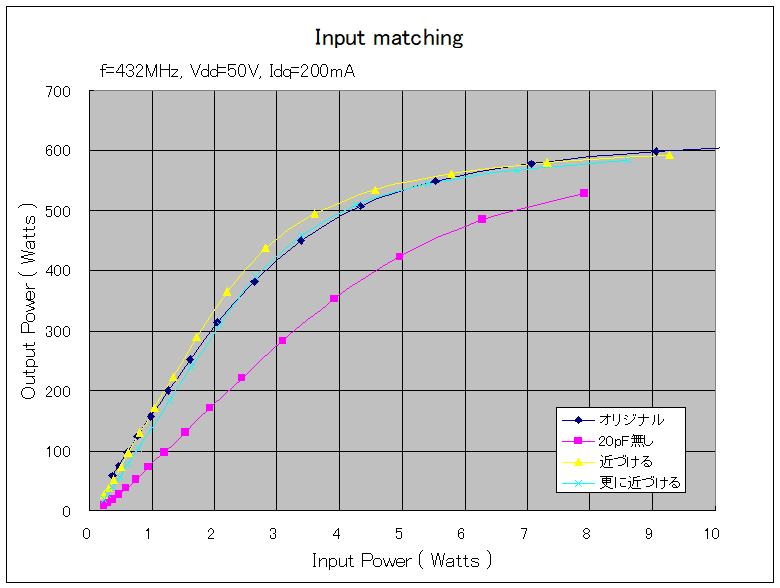

と、ここまで書いたのですがIRLの差による特性の差異が気になったので、簡単に入力側に調整用に追加(回路シュミレーションでは入っていない)した20pFの有無、および位置をずらした場合のデータを取ってみました。

『オリジナル』というのは上の方でデータ取得している状態です。調整用の20pFの位置などを動かすと、PAのIRLが変化するため被測定PAとSG間に入っているドライバー用アンプ(自作のアンプですが広帯域設計のためアイソレータが入っていません)の負荷インピーダンスが変化するためSGからの出力は同じでもドライバーアンプの出力が変わってしまっているのはご愛敬です。

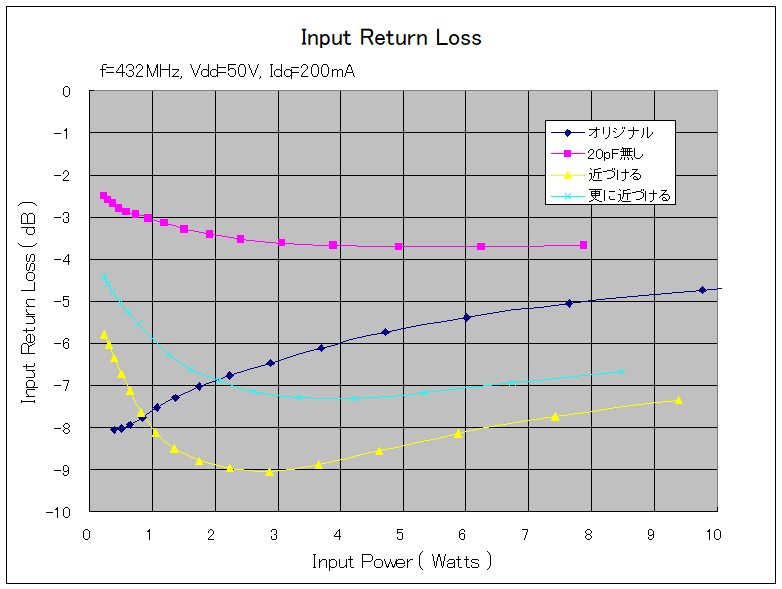

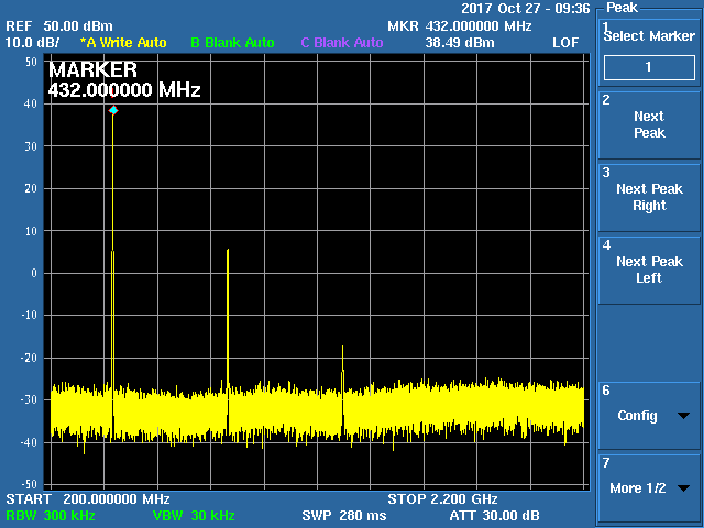

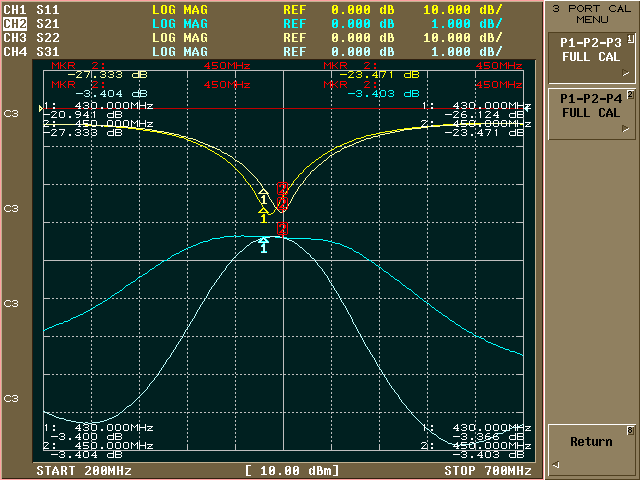

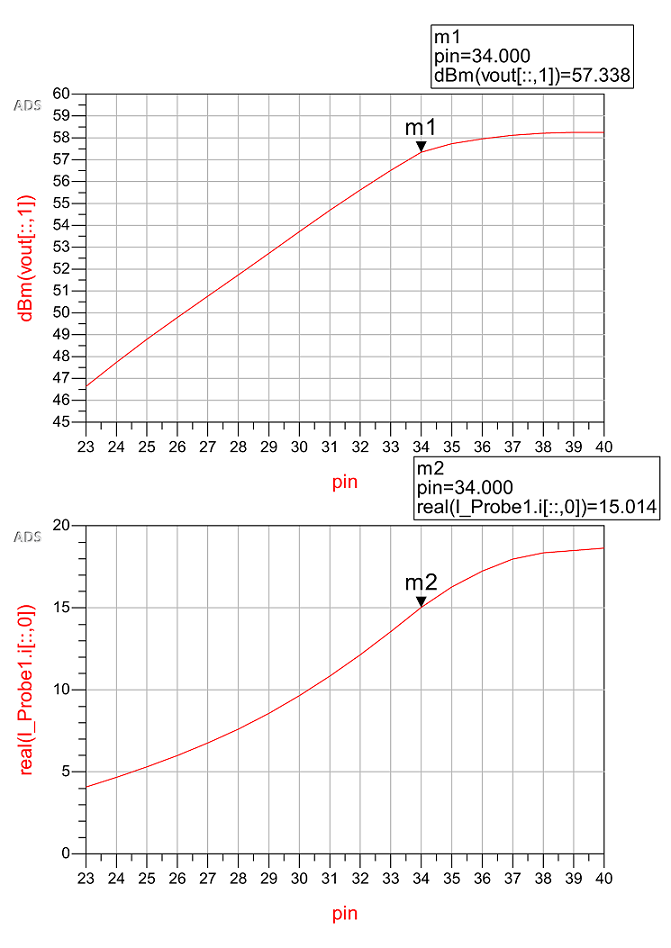

IRLの変化としてまとめたグラフです。

IRL特性的にはさんざんな状態ですが、下記の事が再認識できます。

1.IRLは良い方がGainも高い → 黄色線の特性が顕著

2.入力(出力)に対してのIRL特性が飽和特性に影響を与える

→ピンク色線ですが、IRLの絶対値は悪いですが出力に応じでIRLが悪化してこない。結果、飽和特性はソフトサチュレーション特性である

3.青色線(オリジナル)はIRL特性のように小信号域ではGainも高いが、IRLが悪化してくる領域ではGainも低下してくる。ただし、この状態が1番ドライバーアンプの出力が大きくなる(決して50Ωに整合されているという意味ではありません。)